|

|

|

|

|

|

|

单机架即可实现地球模拟器的性能 日本开发Peta计算机用超高速加速器LSI(图)<%=id%> |

|

|

|

target=_blank>

加速器“GRAPE-DR”

. .

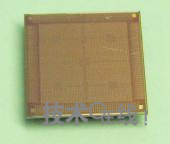

GRAPE-DR芯片

. .

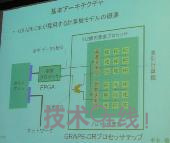

基本架构

. .

试制的加速卡

... 日经BP社2006年11月10日报道. 日本东京大学和日立国立天文台开发出了单精度时运算速度达512GFLOPS、双精度时达384GFLOPS的加速器“GRAPE-DR”,其运算性能达到了由索尼集团、东芝和IBM共同开发的微处理器“Cell”的2倍以上。与通用微处理器配合使用,能够起到提高系统运算速度的作用。其电力效率高,每个加速器最大功耗为60W。

... GRAPE-DR是由东京大学信息工程系研究科教授平木敬领导的研究小组,和国立天文台理论研究部教授、天文模拟项目负责人牧野淳一郎领导的研究小组联合开发的。“目的是开发快速、廉价、易用的超级计算机”(平木)。

... 为此,编译器也进行了自主开发。利用现在的试制版和GRAPE-DR实机已经证实能够正常运行。GRAPE-DR不同于东京大学过去开发的面向特定用途的加速器“GRAPE”系列,能够用于普通的科学技术运算。“在超级计算机排名‘500强(TOP500)’中使用的Linpack基准程序测试中也显示出了高水平”(平木)。

... 在单芯片上配置512个运算器

... GRAPE-DR在17mm×17mm的芯片上配置了512个称为“PE”的运算器。具体来说,由32个PE组成的子块排列 16个方格上,构成一个加速器。各PE均具备执行“SIMD(single instruction stream-multi data stream,单指令多数据流)”指令的功能,具有和Cell配备的8个运算器相同的作用。不过,和Cell不同的是并未在芯片上配备运行操作系统的通用微处理器功能。只能通过内存控制器FPGA,将英特尔等微处理器接到该加速器上,才能作为运算系统使用。

... 该加速器采用90nm工艺CMOS技术设计。工作频率为500MHz。晶体管数量约3亿个,比AMD生产的“AMD D Opteron”还多。由台积电代工生产。

... 今后准备在2007年度内通过合作厂商以每块100万日元的价格销售运算性能达1TFLOPS的加速卡。如果采用该加速器构筑小型超级计算机,“利用1个机架、约5000万日元的成本即可实现和Linpack基准测试值约35TFLOPS的地球模拟器相同的性能”(平木)。2008年度计划利用相当于40个机架、4000个GRAPE-DR的系统,实现运算性能达2PFLOPS的全球最高水平。包括通用微处理器在内,整个系统的耗电量为500kW。构筑成本预计“约10亿日元,非常便宜”(平木)。

... 另外,平木等人还制定了2010年前后实现“20~40PFLOPS”的目标。平木表示:“如果设计工艺采用45nm CMOS技术的话,就能制造单芯片3~4TFLOPS的加速器。能否实现将取决于预算。”据悉开发目标是2008年~2010年荣登TOP500第一位。

.

中国科技资讯网

|

|

|

|

|

设为首页 | 加入收藏 | 广告服务 | 友情链接 | 版权申明

Copyriht 2007 - 2008 © 科普之友 All right reserved |